Examen VHDL 1ere session 2010

Exercice 1 : Conception d'un système de gestion de parking (3 points)

Le but de notre système est de gérer la disponibilité des places de parking. Ce système possède 4 signaux d’entrée (mode in) les captures d’entrée-sortie de type std_logic, l’horloge et le nombre maximal de places dans le parking (mot binaire de 4 bits de type std_logic_vector). Les entrées capteurs servent à incrémenter ou à décrémenter le compteur (4 bits). La sortie de compteur est comparée au nombre maximal de places dans le parking.

Les signaux de sortie (mode out) sont :

PD = 1 s’il reste des places disponibles si non PD=0 (type std_logic).

PC= 1 si le parking est complet si non PC=0 (type std_logic).

- Ecrire l’entité qui décrit la vue externe de ce système.

- Donner l’architecture comportementale en utilisant un process et de l’affectation conditionnelle. Utilisez dans le process l’instruction if…. Then…..elsif...

Exercice 2 : Communication par liaison série (6 points)

Il s’agit de réaliser à partir d’un code source en VHDL une communication par liaison série entre deux module, voir schéma ci-dessous.

I– Réalisation du MODULE A

1. Diviseur:

Ce sous module assure la division de l’horloge HOR à 48 MHz afin d’obtenir un signal de fréquence 10 kHz permettant de cadencer l’envoi de chaque bit.

Réaliser ce diviseur à partir de 3 compteurs 8 bits. Utilisez pour cela 3 variables (COUNT_0, COUNT_1, COUNT_2) de type integer, représentant chacune la valeur d’un compteur.

2. Compteur Front Montant/Front Descendant :

Grâce à ce sous module, on compte les différents fronts montant et descendant de l’horloge 10 KHz afin de pouvoir positionner la sortie clk au repos (clk = 0) ou active (horloge 10 kHz).

Dans notre cas, la sortie clk se positionne au repos (niveau logique 0) lorsque 8 fronts montant et descendant auront été comptés (correspondant à l’envoi de 8 bits). La sortie clk sera à nouveau active si le signal raz est actif (envoi d’une nouvelle donnée).

Décrire le comportement en VHDL de ce sous module.

3. Sérialisation :

Ici, ce module effectue la sérialisation de la donnée 8 bits présente sur donnée Din, cette donnée est sérialisée grâce au cadencement 10kHz (clk) du sous module sérialisation.

Pour se faire on va procéder par décalage du bus donné. C'est-à-dire que le bit 0 (LSB) va être envoyé, ensuite on décale les bits 8 à droite et nous répétons cela 7 fois. On aura, au total, envoyé nos 8 bits de commande un à un. La sortie du module A nommé data.

Donnez la description en VHDL synthétisable de ce registre à décalage à droite chargement parallèle synchrone.

II- Réalisation du MODULE B :

Le module B nous permettra de réceptionner la donnée série émise par le module A puis de l’envoyer à l'afficheur lcd. Le module permet simplement la désérialisation des données reçus par le Module A nommée data et qui a été envoyé grâce à l’horloge clk. RAZ remise à zéro (1 bit) asynchrone actif au niveau bas (‘0’).

Faire une description en langage VHDL (entity et architecture) d’un registre série-parallèle à 8 bits pour le module B.

Exercice 3 : Diagramme d’état d’un circuit asynchrone (4 points)

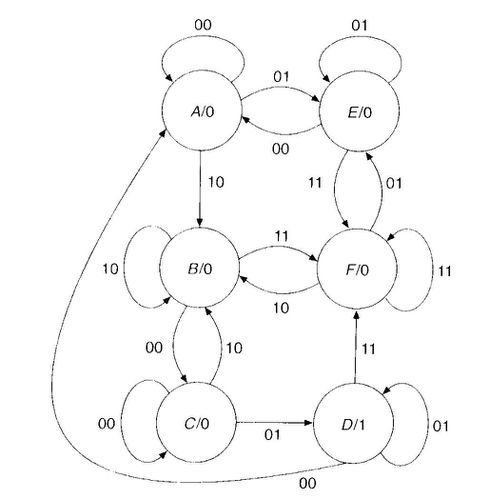

Le système à concevoir dispose deux entrées R et P et une sortie Q. Les valeurs d'entrée sont indiquées sur les arcs, les noms de l'état et les valeurs de sortie des états stables sont indiquées dans les cercles. Sans oublier l’entrée d’horloge qui fait avancer le processus, et celle de remise à zéro qui permet de l’initialiser le système: L’état initial est l’état A.

La description du système se fait par un nombre fini d’états. Ci-dessous la représentation schématique d’un système à 6 états (A, B, C, D, E et F) :

Donner la description en langage VHDL (Entité et Architecture) de ce système en se basant sur le diagramme d’état. Le système est actif sur front montant.

/image%2F1390533%2F20211218%2Fob_91a15e_20211218-204256.jpg)

/https%3A%2F%2Fassets.over-blog.com%2Ft%2Fcedistic%2Fcamera.png)

/image%2F1390533%2F20201123%2Fob_f3135e_zvosbvosv.png)

/image%2F1390533%2F20201123%2Fob_03c20d_efahc.png)