Series d'exercices 9 - VHDL

Exercice 1: Évaluer le signal “S1” et la sortie "Out1"lors d'exécution du code VHDL suivant.

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY PartB IS

PORT (In1, In2, Pb1: IN STD_LOGIC;

Out1: OUT STD_LOGIC);

END PartB;

ARCHITECTURE PartB_Arch OF PartB IS

SIGNAL S1 : std_logic := '1';

BEGIN

b1: BLOCK (Pb1='1')

BEGIN

S1 <= GUARDED NOT In1;

Out1 <= NOT In1 OR Not In2;

END BLOCK b1;

END PartB_Arch;

|

In1 |

1 |

|

In2 |

0 |

|

Pb1 |

0 |

|

S1 |

? |

|

Out1 |

? |

Exercice 2:

On considère un convertisseur d'un nombre binaire de n-bits en un nombre décimal.

A.

Prenez le cas pour n = 3, la table de conversion est donnée comme suivante:

|

Entrée |

Sortie |

||

|

a(2) |

a(1) |

a(0) |

Z |

|

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

|

0 |

1 |

0 |

2 |

|

0 |

1 |

1 |

3 |

|

1 |

0 |

0 |

4 |

|

1 |

0 |

1 |

5 |

|

1 |

1 |

0 |

6 |

|

1 |

1 |

1 |

7 |

- Ecrire la description en VHDL de l'entité, CONVERTER3, d'un convertisseur de 3-bits.

- Écrire le comportement architecture, FUN3, d'un convertisseur de 3-bits en utilisant l'instruction WITH. . . SELECT. . . WHEN.

B.

On désire d'écrire un code VHDL pour le cas général d'un convertisseur binaire de n-bits en décimal, avec n est un entier positif.

L'entrée a est de type BIT_VECTOR de taille (n).

La sortie Z est INTEGER qui peut être calculée à partir de la relation suivante:

Z = a 0 * 2 0 + a 1 * 2 1 + a 2 * 2 2 +⋯+ a n -1 * 2 n -1

- Ecrire la description d'entité, CONVERTERn, d'un convertisseur de n-bits. Assurer que la déclaration de la paramètre n pour le modèle GÉNÉRIQUE est de type POSITIVE et est initialisée à la valeur 16.

- Ecrire l’architecture, FUNn, d'un convertisseur de n-bits.

- Assurer l''utilisation de PROCESS

- Dans le processus, déclarer la variable Temp et initialiser à 0, puis pour chaque bit i, tester le bit a (i) lorsqu'il est égal à '1', la valeur Temp s'incrémente de 2i pour avoir cette conversion à l'aide de l'instructions for ....loop et if ... then.

- Notons que xy peut être écrit en VHDL sous la forme suivante: x ** y.

- Enfin attribuer la valeur de Temp à Z.

Exercice 3:

On considère un système possède deux entrées l'horloge CLOCK et l'entrée d’activation « START » et délivre à la sortie un signal PULSE à des intervalles réguliers. Ce système s’exécute en cycle d’horloge à travers 16 périodes : et

- Si l'entre d'activation START est mise a ‘1’, affirme une "PULSE" sur le cycle d’horloge 1, 7, 8, 15, sinon PULSE est mise à ‘0’.

- Si l'entrée START est mise a ‘0’, PULSE n’est pas mis à jour.

Donner la description comportementale en VHDL de ce système.

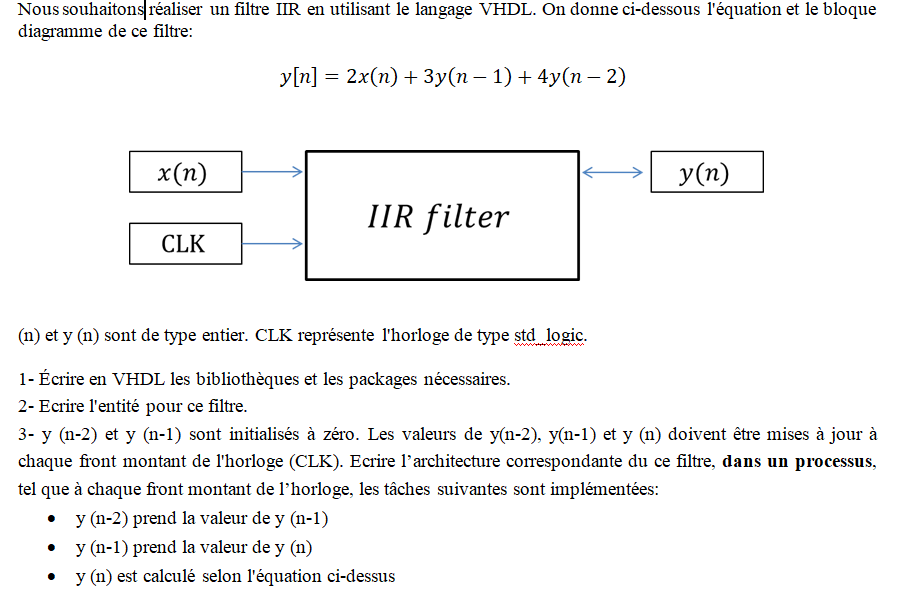

Exercice 4: Filtre numerique IIR en VHDL

Exercice 5:

On considère un système qui compte le nombre d'occurrences de '0' dans un nombre de N bits.

Le système comprend:

- Une entrée, nommée In1,de type std_logic_vector de N-bit;

- Une sortie, nommée Out1, de type entier.

Voici un exemple montre le résultat du programme pour différentes entrées de N- bits (N = 5).

|

In1 |

"11101" |

"01011" |

"00000" |

"11111" |

|

Out1 |

1 |

2 |

5 |

0 |

- Ecrire l'entité du système en tenant compte de la valeur N comme un paramètre générique positif qui est égale à 5.

- Ecrire une fonction appelée “Occurrence” qui prend un argument X de type std_logic_vector de N-bit. La fonction devrait compter le nombre d'occurrences de '0' en X et le renvoyer en sortie appelée Y.

- Ecrire l’architecture du système. L'architecture devrait appeler la fonction“Occurrence”décrite dans la partie b afin de mettre à jour la sortie Out1.

Exercice 6:

On désire de concevoir un registre a 4 bits implémenter à partir des multiplexeurs et des bascules D. Ce registre 4 bits a 2 entrées de sélection s1 et s0, 4 entrées de donnée I3 .. I0, et 4 sorties Q3 .. Q0.

Si s1s0 = 00 cela signifie maintenir la valeur de l’état présent, cas d'un registre de mémorisation,

s1s0 = 01 signifie un chargement parallèle,

s1s0 = 10 signifie la remise mise a zéro de la sortie Qi.

s1s0 = 11 décalage à gauche décalé de 1 rang vers la gauche, par exemple 0101 devient 1010 et 1000 devient 0001.

- Décrire en langage VHDL (entité et l'architecture) du premier composant de la Multiplexeur 4:1.

- Décrire en langage VHDL (entité et l'architecture) du second composant de la bascule D.

- L’interconnexion des deux composants s’effectue au travers d’une nouvelle architecture pour l’entité registre. La liaison des deux composants s’obtient au travers des noms de signaux internes représentant un fil (une soudure, un câble) la sortie de multiplexeur et l’entrée du bascule. Donner l'entité et l'architecture global de registre.

Exercice:

L'unité logique arithmétique (UAL) est l'organe et le composant le plus important dans l'unité centrale de traitement UCT. Il exécute normalement des opérations logiques et arithmétiques telles que l'addition, la soustraction, la multiplication, la division, décalage, les fonctions logiques etc. Le fonctionnement typique de l’UAL est représenté comme indiqué dans le diagramme ci-dessous,

Comme vous le constatez, l'UAL reçoit deux opérandes à l'entrée 'A' et 'B' de 8 bits. Le résultat est noté 'UAL_S', qui a également de taille de 8 bits. Le signal d'entrée 'Sel' est une valeur de 4 bits qui indique à l'UAL l'opération doit être effectuée selon 16 opérations logiques possibles. Tous les signaux sont de type "std_logic". Les opérations logiques et arithmétiques en cours d'implémentation dans l'UAL sont les suivantes:

a) Ecrire l'entité en code VHDL pour l'UAL.

b) Ecrire l'architecture de l'UAL pour implémenter ses fonctions dans le processus.

/image%2F1390533%2F20211218%2Fob_91a15e_20211218-204256.jpg)

/https%3A%2F%2Fassets.over-blog.com%2Ft%2Fcedistic%2Fcamera.png)

/image%2F1390533%2F20201123%2Fob_f3135e_zvosbvosv.png)

/image%2F1390533%2F20201123%2Fob_03c20d_efahc.png)