Examen VHDL 1ere session 2008

Exercice 1 : (10 points)

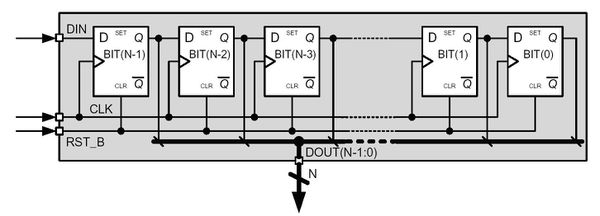

Il s’agit de développer un modèle structurel d’un registre N bits avec une entrée série et une sortie parallèle basé sur les composants des bascules D.

L’entrées: Horloge CLK (1 bit), reset RST_B remise à zéro (1 bit) asynchrone actif au niveau bas (’0’), données série DIN (1 bit) et les Sorties: Contenu du registre DOUT (N bits). N un paramètre générique. Faire une description structurelle en langage VHDL (entity et architecture) d’un registre Registre série-parallèle à 16 bits (voir shéma ci-dessus) . L’usage d’une instruction generate est requise.

Exercice 2: (5 points)

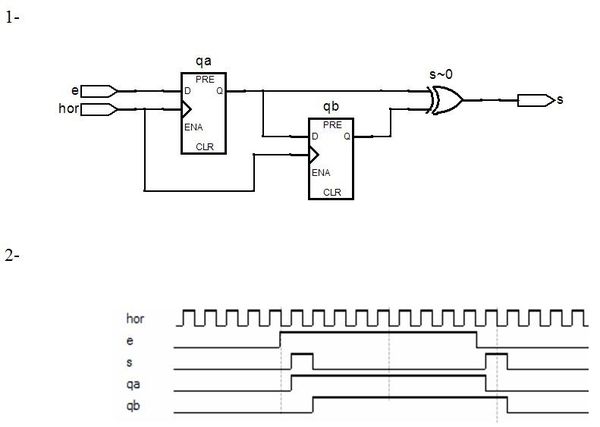

On considère le programme ci-dessous (écrit en VHDL) :

Library ieee;

use ieee.std_logic_1164.all;

entity transitm is port ( clk, e : in bit ;

s : out bit );

end transitm ;

architecture quasi_struct of transitm is

signal qa, qb : bit ;

begin

schem : process (clk)

begin

If ( clk'event and clk = '1') then

qa <= e ;

qb <= qa ;

end if;

end process schem ;

s <= qa xor qb ;

end quasi_struct ;

- Déduire de ce programme, par une construction méthodique, un schéma (bascules

et portes logiques).

- Compléter le chronogramme ci-dessous.

Exercice 3 : (5 points)

Le système à concevoir dispose de deux entrées et de deux sorties. Les entrées sont l’horloge clk et la commande C ; les sorties sont S1 et S2. Les entrées et les sorties sont de type std_logic sauf C est de type bit. Le système est actif sur front descendant. Le système répond au chronogramme suivant :

Donner la description en langage VHDL (Entity et Architecture) de ce système en utilisant un process. Dans le process, utiliser l’instruction case …. is when, et l’instruction if ….. then …. else.

Correction

Exercice1:

Library ieee;

use ieee.std_logic_1164.all;

Entity D_RAZ is port

(D, clk, CLR : in std_logic;

Q : out std_logic);

End D_RAZ;

Architecture arch_D_RAZ of D_RAZ is

Begin

process (clk, CLR)

Begin

IF (CLR='0') then Q<='0';

ELSIF (clk'event and clk = '1') then Q<=D;

END IF;

END process;

END arch_D_RAZ;

Library ieee;

use ieee.std_logic_1164.all;

entity registre is port

(DIN, clk, REST_B : in std_logic;

DOUT : out std_logic_vector (15 downto 0));

End registre;

architecture arch_registre of registre is

component D_RAZ port (D, clk, CLR : in std_logic;

Q : out std_logic);

end component;

signal S : std_logic_vector (15 downto 0);

constant Nb_bits : integer :=15;

begin

cellule : for i in Nb_bits downto 0 generate

cellule_16 : if i = Nb_bits generate

D_RAZN_1 : D_RAZ port map ( DIN, clk, REST_B,S(15));

DOUT(i)<=S(i);

end generate cellule_16;

cellule_int : if (i<Nb_bits and i >0 ) generate

D_RAZint : D_RAZ port map ( S(i+1), clk, REST_B,S(i));

DOUT(i)<=S(i);

end generate cellule_int;

cellule_0 : if (i=0 ) generate

D_RAZ0 : D_RAZ port map ( S(i+1), clk, REST_B,S(i));

DOUT(0)<=S(0);

end generate cellule_0;

end generate cellule;

end arch_registre;

Exercice2:

Exercice 3 :

Library ieee;

use ieee.std_logic_1164.all;

entity seq is port (clk: in std_logic;

C: in bit; S1,S2: out std_logic);

end seq;

architecture arch_seq of seq is

signal Etat : std_logic_vector (2 downto 0);

begin

process (C,clk)

begin

if (clk' event and clk ='0') then

case Etat is

when "000" => S1<='0' ; S2<='0';

if C='1' then Etat <= "001";

else Etat <= "000";

end if;

when "001" => S1<='1' ; S2<='0';

if C='0' then Etat <= "010";

else Etat <= "001";

end if;

when "010" => S1<='1' ; S2<='1';

if C='0' then Etat <= "011";

else Etat <= "001";

end if;

when "011" => S1<='0' ; S2<='1';

if C='0' then Etat <= "100";

else Etat <= "001";

end if;

when "100" => S1<='0' ; S2<='0';

if C='0' then Etat <= "000";

end if;

When others => Etat <= "000";

end case;

end if;

end process;

end arch_seq;

/image%2F1390533%2F20211218%2Fob_91a15e_20211218-204256.jpg)

/https%3A%2F%2Fassets.over-blog.com%2Ft%2Fcedistic%2Fcamera.png)

/image%2F1390533%2F20201123%2Fob_f3135e_zvosbvosv.png)

/image%2F1390533%2F20201123%2Fob_03c20d_efahc.png)